Product Summary

The AX88772ALF is a Low-pin-count USB 2.0 to 10/100M Fast Ethernet controller. The AX88772ALF is a high performance and highly integrated ASIC which enables low cost, small form factor, and simple plug-and-play Fast Ethernet network connection capability for desktops, notebook PC’s, Ultra-Mobile PC’s, docking stations, game consoles, digital-home appliances, and any embedded system using a standard USB port. The AX88772ALF provides an optional External Media Interface (EMI) for external PHY or external MAC for different application purposes. The EMI can be a media-independent interface (MII) for implementing 100BASE-FX Ethernet or HomePNA functions. The EMI can also be a Reverse-MII or Reverse Reduced-MII (Reverse-RMII) for glueless MAC-to-MAC connections to any MCU with Ethernet MAC MII or RMII interface.

Parametrics

AX88772ALF absolute maximum ratings: (1)Digital core power supply:-0.3V to 2.16V ; (2)Analog Power. 1.8V:-0.3V to 2.16V ; (3)Power supply of 3.3V I/O:-0.3V to 4V ; (4)Power supply of on-chip voltage regulator:-0.3V to 4V ; (5)Analog Power 3.3V for Ethernet PHY bandgap:-0.3V to 3.8V ; (6)Analog Power 3.3V for USB PLL.:-0.3V to 4V ; (7)Analog Power 3.3V for USB TX and RX:-0.3V to 4V ; (8)Input voltage of 1.8V I/O:-0.3V to 2.16V; (9)Input voltage of 3.3V I/O:-0.3V to 4.0V ; (10)Input voltage of 3.3V I/O with 5V tolerant:-0.3V to 5.8V ; (11)Storage temperature: -40℃ to 150℃ ; (12)DC input current:20mA ; (13)Output short circuit current: 20mA.

Features

AX88772ALF features: (1)Integrates 10/100Mbps Fast Ethernet MAC/PHY; (2)IEEE 802.3 10BASE-T/100BASE-TX compatible; (3)Supports twisted pair crossover detection and auto-correction (HP Auto-MDIX); (4)Embedded 16KB SRAM for RX packet buffering and 8KB SRAM for TX packet buffering; (5)Supports both Full-duplex with flow control and Half-duplex with backpressure operation; (6)Supports 2 VLAN ID filtering, received VLAN Tag (4 bytes) can be stripped off or preserved; (7)MAC/PHY loop-back diagnostic capability; (8)Integrates on-chip USB 2.0 transceiver and SIE compliant to USB Spec 1.1 and 2.0; (9)Supports USB Full and High Speed modes with Bus-Power or Self-Power capability; (10)Supports 4 or 6 programmable endpoints on USB interface; (11)High performance packet transfer rate over USB bus using proprietary burst transfer mechanism (submitted for US patent application); (12)Supports USB to Ethernet bridging or vice versa in hardware.

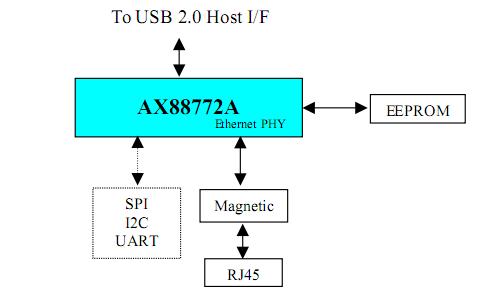

Diagrams

|

AX88140A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

AX88172 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

AX88172A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

AX88178 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

AX88178 L |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

AX88180 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))